Sensors and Actuators 74 (1999) 161-168

# Wafer bonding for microsystems technologies

U. Gösele <sup>a,b,\*</sup>, Q.-Y. Tong <sup>a,b</sup>, A. Schumacher <sup>a</sup>, G. Kräuter <sup>a</sup>, M. Reiche <sup>a</sup>, A. Plößl <sup>a</sup>, P. Kopperschmidt <sup>a</sup>, T.-H. Lee <sup>b</sup>, W.-J. Kim <sup>b</sup>

> <sup>a</sup> Max-Planck-Institute of Microstructure Physics, Weinberg 2, D-06120 Halle, Germany <sup>b</sup> Wafer Bonding Laboratory, School of Engineering, Duke University, Durham, NC 27708-0300, USA

## Abstract

In microsystems technologies, frequently complex structures consisting of structured or plain silicon or other wafers have to be joined to one mechanically stable configuration. In many cases, wafer bonding, also termed fusion bonding, allows to achieve this objective. The present overview will introduce the different requirements surfaces have to fulfill for successful bonding especially in the case of silicon wafers. Special emphasis is put on understanding the atomistic reactions at the bonding interface. This understanding has allowed the development of a simple low temperature bonding approach which allows to reach high bonding energies at temperatures as low as 150°C. Implications for pressure sensors will be discussed as well as various thinning approaches and bonding of dissimilar materials. © 1999 Elsevier Science S.A. All rights reserved.

Keywords: Wafer bonding; Fusion bonding; Pressure sensors; Interface reactions; Hydrophilic bonding; Hydrophobic bonding

# 1. Introduction

'Wafer bonding' refers to the phenomenon that mirrorpolished, flat and clean wafers of almost any material, when brought into contact at room temperature, are locally attracted to each other by van der Waals forces and adhere or 'bond' to each other. This phenomenon has been known for a long time for optically polished pieces of materials and was first investigated for polished pieces of quartz glass by Lord Rayleigh in 1936 [1]. Only in the early 1980s almost simultaneously an attempt was made by researchers at Toshiba [2] and IBM [3] to use this room temperature adhesion phenomenon coupled with an appropriate heating step for silicon wafers in order to replace epitaxial growth of thick silicon wafers or to fabricate Silicon-On-Insulator (SOI) structures, respectively. Shortly afterwards, as an extension of the well established 'anodic bonding', the bonding of structured silicon wafers was applied for the fabrication of micromachined pressure sensors and termed 'silicon fusion bonding' [4]. Wafer bonding can simply be used as a specific joining technique for all kinds of applications not only in the growing area of microsystems technology which is the subject here, but

also in the area of non-linear optics and light-emitting diodes. Wafer bonding approaches are not restricted to silicon/silicon bonding but may be applied to all kind of material combinations involving silicon or other materials [5]. The availability of a variety of precision thinning approaches discussed later allows the transfer of thin layers from one wafer to another.

In the following, we will first discuss the best investigated and understood case of silicon/silicon wafer bonding including an annealing step (Section 2) and then turn to the atomic reactions at the bonding interface (Section 3), thinning procedures (Section 4) and bonding of dissimilar materials (Section 5). Since the literature on wafer bonding is fairly extensive we will not try to be exhaustive in terms of references but refer to recent conference proceedings [6-9], review articles [10-15], a special 1995 issue of the Philips Journal of Research [16] and a book on this subject [17].

# 2. Silicon wafer bonding and heat treatments

The fabrication of materials combinations in microsystems technologies by wafer bonding usually consists of a number of basic steps which will be outlined and detailed for the case of silicon wafers.

<sup>\*</sup> Corresponding author. Tel.: +49-345-5582657; Fax: +49-345-5582566; E-mail: goesele@mpi-halle.mpg.de

(i) The surfaces of two mirror-polished silicon wafers, which may or may not contain structures such as cavities are conditioned and prepared for the bonding process. The wafers may be thermally oxidized or just contain a native oxide which is made hydrophilic by a proper surface treatment. The wafer surfaces are then typically covered by one or two monolayers of water. The surfaces may also be activated additionally by an appropriate plasma treatment. The surface oxide may also be removed by a dip in hydrofluoric acid which leads to a hydrophobic hydrogen coverage of the silicon surfaces.

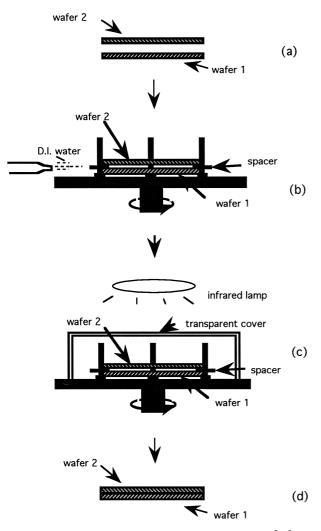

(ii) The two mirror-polished wafer surfaces are brought into contact at room temperature in air either in a conventional cleanroom of class 10 or better or in a so-called microcleanroom (Fig. 1) [18] in order to avoid particles between the wafers. Equipment to perform aligned wafer bonding and/or wafer bonding in vacuum is also commercially available. Usually the bonding is initiated at a certain point by slightly pressing the wafers together locally. The bonded area then spreads over the whole wafer in a couple of seconds.

Fig. 1. Schematic of microcleanroom setup and procedure [18].

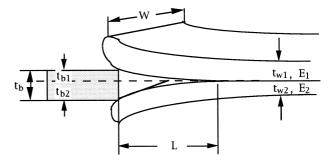

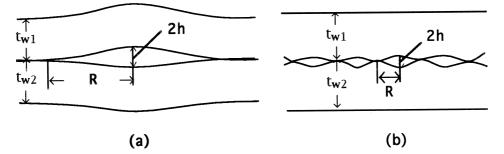

Fig. 2. Schematic of crack-opening method to determine bonding or surface energy.

(iii) Directly after room temperature bonding, the adhesion between the two wafers is determined by van der Waals interactions or hydrogen bridge bonds and one or two orders of magnitude lower than typical for covalent bonding. For most practical applications, a higher bond energy is required which may be accomplished by an appropriate heating step. This heating step is frequently performed at temperatures as high as 1100°C. Treatments at intermediate temperatures or even at room temperature are also possible if performed properly, as will be discussed later.

(iv) For many (but not all) applications, one of the bonded wafers has to be thinned down to a thickness between about 100 nm to some micrometers depending on the specific application. Many different approaches have been developed to accomplish this thinning requirements as will be discussed later.

In the following, we will comment on some selected specific questions associated with the above steps.

Whether two wafers bond depends on the bonding energy at room temperature and the roughness and waviness of the two wafers. The bonding energy may be characterized by the energy associated with opening the surface by the so-called crack-opening method first described by Maszara et al. [19] and schematically shown in Fig. 2. In the case of bonded pairs with identical wafers of thickness  $t_w$  and  $E_1 = E_2 = E$ , where E is Young's modulus, the expression for the surface energy per area  $\gamma$  is

$$\gamma = \frac{3Et_{\rm w}^3 t_{\rm b}^2}{32L^4} \tag{1}$$

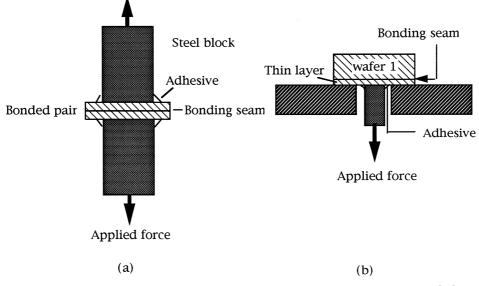

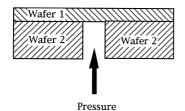

The various parameters are given in Fig. 2. For wafers of different thickness and/or elastic properties, analogous formulae are available [20]. Eq. (1) holds only for unstructured wafers. For structured wafers (e.g., with cavities) only a fraction  $f_b$  of the surface area is available for bonding and  $\gamma$  in Eq. (1) has to be replaced by  $\gamma f_b$ . Other arrangements for mechanical testing are shown in Figs. 3 and 4. The arrangement shown in Fig. 3a does not give the surface energy but the tensile strength which strongly depends on microcracks and sample preparation.

Fig. 3. Schematic of different methods of testing of mechanical properties of bonding interfaces [17].

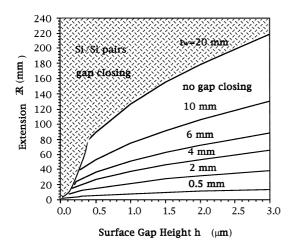

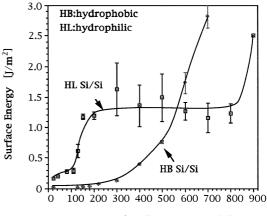

The surface energy  $\gamma$  is typically around 100 mJ/m<sup>2</sup> for hydrophilic surfaces and around 20 mJ/m<sup>2</sup> for (hydrogen covered) hydrophobic silicon surfaces generated by an HF dip [21,22]. It is nowadays also possible to calculate at least approximately whether wafers with a certain waviness and roughness will bond or not [17]. For these calculations, let us assume gaps between wafers caused by a flatness nonuniformity with a lateral extension *R* (or spatial period 2*R*) much larger than their depth (or gap height) *h* as schematically shown in Fig. 5. The condition for gap closing depends on the ratio of *R* to the wafer thickness  $t_w$ .

For  $R > 2t_w$  (Fig. 5a), the condition for gap closing depends on wafer thickness  $t_w$  and is given by

$$h < \frac{R^2}{\sqrt{\frac{2}{3}\frac{E't_{\rm w}^3}{\gamma}}} \tag{2}$$

where E' is given by  $E/(1 - \nu)$  with  $\nu$  being Poisson's ratio. For  $R < 2t_w$  (Fig. 5b), the condition for gap closing is independent of wafer thickness  $t_w$  and given by

$$h < 3.6 (R\gamma/E')^{1/2}$$

(3)

In Fig. 6 the regions of gap closing or not closing are shown for two silicon wafers of equal thickness  $t_w$  based

Fig. 4. Test structure to measure bonding or surface energy.

on  $\gamma = 100 \text{ mJ/m}^2$  and for various different values of  $t_w$ . For structured wafers, in expressions (2) and (3),  $\gamma$  may approximately be replaced by  $\gamma f_b$ .

In practice, the flatness variation of  $1-3 \ \mu m$  over commercial 4-in. silicon wafers poses no obstacle for wafer bonding at room temperature because the deformation of the two wafers can easily accommodate this scale of surface waviness. Bow and warpage of wafers up to about 25 µm are also tolerable. The above expressions may be used to predict whether wafer bonding is possible provided  $\gamma$  and the waviness of the surface are known. In reality the waviness is represented in a whole Fourier spectrum of amplitudes for certain wavelengths. If not only one single spatial frequency (like the macroscopic bow) is dominating, an integral formulation has to be used. The developed theoretical expressions also show that even infinitely thick pieces can be bonded provided the surface flatness is sufficiently good [23] as has been known to occur for optically polished bulk pieces of glasses or metals since almost hundred years.

For bonding a standard silicon wafer to a silicon wafer with cavities, the above equations can also be used to predict whether the parts of the unstructured wafer covering the cavities will bond to the bottom of the cavity [17].

The room temperature bonding step may either be performed in air under normal pressure or under vacuum conditions, as may be dictated by the requirement of evacuated cavities for various micromechanical sensors. Bonding even under reduced pressure (low vacuum) is helpful in bonding wafers with high surface roughness. Bonding in different atmospheres such as oxygen or nitrogen is also possible. The different behavior of the bonding or surface energy for hydrophobic and hydrophilic silicon wafers as a function of heat treatment temperature for extended times of many days after room temperature bond-

Fig. 5. Schematic of surface waviness.

ing in air is shown in Fig. 7. It can be seen that for hydrophilic surfaces about half of the full bonding energy can be reached already at temperatures around 150°C. Bonding in (low) vacuum allows to reach almost full bonding energy [24] at such low temperatures.

## 3. Reactions at bonding interfaces

There is a clear trend towards wafer bonding applications in micromechanics and microelectronics which do not allow annealing of the bonded structure at high temperatures, since the structure either contains temperature sensitive device or metallization layers or consists of different materials with vastly different thermal expansion coefficients. In order to address these needs of low temperature bonding processes, we systematically investigated the atomistic processes occurring at the bonding interface for different surface chemistries. We will not discuss here the also promising low temperature bonding approach based on a plasma treatment of the silicon surfaces [25–27].

Most silicon wafers used for wafer bonding are covered with either a thin native oxide (with a thickness of about 2 nm) or a purposely grown thermal oxide (as necessary for SOI substrates or for parts in microsystems which have to be electrically isolated) which has been rendered hy-

Fig. 6. Calculation under which conditions gap closure does or does not occur for different assumed wafer thicknesses from 0.5–20 mm and  $\gamma = 100 \text{ mJ}/\text{m}^2$  [17].

drophilic by a proper cleaning procedure. These oxides are typically covered with a monolayer or two of water molecules adsorbed on OH groups associated with the oxide. These hydrophilic surfaces are very similar to those present on fused quartz. Alternatively, silicon surfaces may be dealt with in diluted HF leading to the removal of native oxide layers and a direct hydrogen coverage of the silicon surfaces which renders the surfaces hydrophobic. Both hydrophilic and hydrophobic silicon wafers may be bonded at room temperature by relatively weak hydrogen bridge or van der Waals bonds. In both cases subsequent heating is required to increase the bonding energy for practical applications. Of course, only hydrophobicly bonded wafers are free of an insulating oxide layer after bonding and annealing.

For hydrophobicly bonded wafers during heating, the reaction consists of sequential hydrogen desorption (depending on the specific bonding configuration) and silicon–silicon covalent bond formation according to

$$\equiv Si - H + H - Si \equiv \Rightarrow \equiv Si - Si \equiv + H_2 \tag{4}$$

At temperatures up to about 500°C, the hydrogen is not diffusing into the silicon but rather diffuses along the bonding interface.

#### Annealing Temperature [°C]

Fig. 7. Saturation values of surface or bonding energy measured by the crack opening method as a function of temperature after long-time heat treatments (up to 100 h) [17].

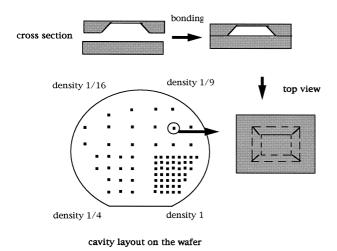

Fig. 8. Cavities used for measuring pressure increase due to interface reactions. (a) Schematic of test structure cavity. (b) Cavity layout on the wafer [31].

In the case of hydrophilic wafer bonding, the end result, namely the generation of molecular hydrogen, is the same but there are intermediate steps involved. Initially there exists molecular water at the interface in terms of monolayers of water adsorbed on hydrophilic oxides. Molecular water will also come partly from the reaction

$$\equiv Si - OH + HO - Si \equiv \Rightarrow = Si - O - Si \equiv + H_2O$$

(5)

which starts to form strong covalent bonds across the bonding interface at temperatures above about 120°C. Molecular water will oxidize the surrounding crystalline silicon and form molecular hydrogen via the reaction

$$\mathrm{Si} + 2\mathrm{H}_2\mathrm{O} \Rightarrow \mathrm{SiO}_2 + 2\mathrm{H}_2 \tag{6}$$

A thin oxide favors reaction (6) and therefore the formation of strong bonds for a given relatively low temperature as compared to the case of much thicker thermal oxides through which the water molecules have to diffuse. On the other hand, the hydrogen molecules resulting from reaction (6) cannot appreciably be dissolved in the silicon and therefore generate a gas pressure at the interface. This pressure, which may lead to formation of interface bubbles or weakening of the interface bonding, decreases with increasing oxide thickness (since the hydrogen can be dissolved in the oxide). Therefore, for strong and high quality bonding a combination of a very thin oxide (which favors getting rid of the water via reaction (6)) and a thick oxide (which reduces the pressure at the interface) appears to be most favorable [28], as indeed was found experimentally [29].

All these reactions can in detail be investigated by Multiple Internal Reflection Spectroscopy which also allows to distinguish different reaction behavior of hydrophobic wafer surfaces of different crystallographic orientations. For details the reader is referred to the excellent articles by the group of Chabal at Bell Laboratories [30].

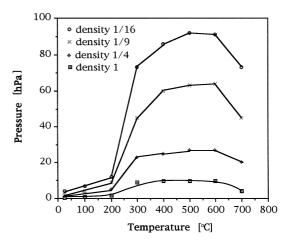

In the present paper we will concentrate on the movement of the reaction product (molecular hydrogen) along the interface which was investigated by Mack et al. [31,32]. For this purpose arrays of cavities of the same size but with different areal densities where fabricated in such a way that the remaining silicon membrane can be used to measure the pressure in the cavities sensitively (Fig. 8). The silicon wafers with cavities where bonded to unstructured silicon wafers either hydrophobicly or hydrophilicly under conditions of high vacuum. The bonded wafers were then heated to different temperatures and the pressure increase was measured later at room temperature as a function of time, heat treatment, and cavity density. An example of the results are shown for hydrophilic wafers in Fig. 9 [31]. It is obvious that the lower density cavities show a higher increase in pressure corresponding to the larger available bonding area around a cavity.

By mass spectrometry the main constituent in the cavities was shown to be molecular hydrogen for both hydrophilic and hydrophobic wafers [32]. The generated hydrogen gas can diffuse along the interface even at room temperature.

For both hydrophilic and hydrophobic bonding a gas pressure will develop in cavities even if the room temperature bonding is performed under high vacuum conditions. This is also true for anodic bonding [32,33] in which case oxygen develops during the bonding procedure. It would be desirable for absolute pressure sensor to avoid any gas development at all. Bonding of clean silicon surfaces without any absorbed layers of water or hydrogen should, in principle, allow this goal to be achieved. Experimentally, clean silicon surfaces require ultra high vacuum (UHV) conditions. We managed recently to obtain large area and self-propagating 4 in. (100) silicon wafer bonding under UHV conditions at room temperature [34,35], although not yet for structures containing cavities. Bonding is so strong, that without any subsequent heat treatment the bonded samples fractured in tensile tests at other locations than the interface.

Fig. 9. Pressure increase in cavities after hydrophilic bonding and annealing at specified temperatures for 70 h [31].

# 4. Thinning procedures

In many cases one of the wafers has to be thinned to create a thin single crystalline silicon layer. Various thinning approaches have been developed and are used in commercial SOI production.

(i) Precision polishing allows the fabrication of layers down to about 1  $\mu$ m with a thickness variation of about 0.3  $\mu$ m over the whole wafer which is good enough for most bipolar applications [36].

(ii) The use of a  $p^+$ -boron-doped silicon epilayers stress compensated by the incorporation of the proper amount of germanium as etch stop layers leads to a very good thickness uniformity also in the 10 nm range [37].

(iii) An etch-stop based on a porous silicon sacrificial layer has been developed with similarly good thickness variations [38].

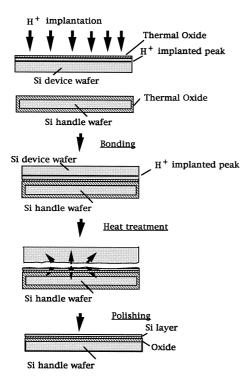

(iv) An especially elegant procedure has been suggested by Bruel and termed SMART-CUT [39,40]. It is based on hydrogen implantation before bonding which leads to the splitting of silicon wafers along hydrogen-filled microcracks induced by the precipitation of the implanted hydrogen during a heating step after bonding. The smart-cut procedure is schematically shown in Fig. 10 [20]. The big advantage of this procedure, which also allows a thickness variation in the 10 nm range, is that split wafers may be reused after some soft polishing (which is also required for the transferred layer) since its thickness has changed only by about a micrometer or less. Co-implantation of a much lower dose of boron allows to decrease the temperature

Fig. 10. Schematic of hydrogen-implantation induced layer splitting ('smart-cut') [17,39].

and/or time of splitting considerably ('smarter-cut' [41]) which is most important for bonding materials of different coefficients of thermal expansion such as silicon and quartz.

Layer splitting by hydrogen implantation and wafer bonding is especially interesting for expensive materials such as single crystalline SiC [42,43], diamond [42], or GaAs [44] for which the smart-cut procedure also works. Repeated transfer of thin layers onto appropriate inexpensive substrates could allow a large decrease in price of these materials and consequently lead to a more widespread and economic usage.

## 5. Bonding of other materials

Most materials, if properly polished and their surfaces properly conditioned, do adhere to each other at room temperature and can thus be used for wafer bonding approaches as has been shown by the group of Haisma at Philips [5,10,16]. The materials are certainly not limited to semiconductors and can be present in single crystalline, polycrystalline or amorphous form. Examples of different material combinations fabricated by wafer bonding include Si on sapphire for improved SOS material [45], crystalline quartz on silicon for high frequency applications [46], Si on fused quartz or glass for HDTV projection masks [47], and GaAs or InP on Si for combining opto- and microelectronics [48–50]. Interesting applications are combinations of different III-V compounds for the fabrication of vertical cavity surface emitting lasers (VCSEL) [51] and lightemitting diodes (LED) [52] pioneered at Hewlett-Packard. For the bonding of III-V compounds the wafer bonding process frequently is performed not at room temperature but at elevated temperatures (around 300-500°C) in flowing hydrogen or at even higher temperatures under the influence of a weight [53,54].

Wafer bonding may be performed via all kinds of intermediate layers such as oxides, nitrides, metals and silicides. Especially important is the bonding via polished polysilicon layers not only for advanced dielectrically isolated (DI) wafers [55] but also for the fabrication of complex three-dimensionally integrated devices or for micromechanics. In this context, the importance of chemomechanical polishing (CMP) should be stressed which nowadays is widely available in microelectronics facilities.

If two different materials are combined, a problem due to a mismatch of the thermal expansion coefficients may arise during the heating step following room temperature bonding. This may lead to debonding, interface sliding or breakage of the bonded pair at elevated temperatures [56]. Only a few cases of interesting materials combinations are known for which the two materials have sufficiently close thermal expansion coefficients. Examples are silicon and silicon carbide, silicon and glasses specifically developed for this purpose and last not least GaAs and sapphire which might become important for combining GaAs based electronics with superconducting microwave devices based on thin films of high temperature superconductors epitaxially grown on sapphire. In the case of GaAs/sapphire bonding the bonding has to be performed at elevated temperatures around 500°C in order to avoid undesirable interface bubbles [57].

# 6. Outlook

Wafer bonding is already established for the industrial fabrication of some sensors, but it is still not as common as anodic bonding. SOI wafers with diameters up to 8 in. fabricated by wafer bonding and various thinning techniques are now commercially available in Japan, the US and Europe. For LEDs wafer bonding or fusion has recently also made its way into production. In many other areas, wafer bonding applications are just in a research or development stage. The development of new techniques such as hydrogen-implantation induced layer splitting is promising also outside of the SOI and even the silicon area.

Wafer bonding offers a new freedom in the design of materials combinations without the common restrictions imposed by the structure (amorphous, polycrystalline, orientation, lattice constant) of the materials to be bonded.

# Acknowledgements

We acknowledge fruitful collaboration with S. Mack, K. Gutjahr, G. Kästner and many others in the area of wafer bonding. Part of the research was supported by grants from SEH Japan to Duke University and from the German Federal Ministry of Science, Education, Research and Technology under contracts BMBF-13N6758/0 and BMBF-13N6451/1. We also acknowledge support by Deutsche Forschungsgemeinschaft.

#### References

- L. Raleigh, A study of glass surfaces in optical contact, Proc. Phys. Soc. A 156 (1936) 326–349.

- [2] M. Shimbo, K. Furukawa, K. Fukuda, K. Tanzawa, Silicon to silicon direct bonding method, J. Appl. Phys. 60 (1986) 2987–2989.

- [3] J.B. Lasky, Wafer bonding for silicon-on-insulator technologies, Appl. Phys. Lett. 48 (1986) 78–80.

- [4] K. Petersen, Silicon fusion bonding for pressure sensors, Proc. IEEE Solid State Sensor Conf., 1988, Hilton Head.

- [5] J. Haisma, B.A.C.M. Spierings, U.K.P. Biermann, A.A.v. Gorkum, Diversity and feasibility of direct bonding—a survey of a dedicated optical technology, Appl. Opt. 33 (1994) 1154–1169.

- [6] U. Gösele, J. Haisma, M. Schmidt, T. Abe (Eds.), First Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 92-7, Electrochem. Soc., Pennington, 1992.

- [7] H. Baumgart, Ch. Hunt, M. Schmidt, T. Abe (Eds.), Second Int. Symp. Semiconductor Wafer Bonding: Science, Technology and

Applications, Electrochem. Soc., Proc., Vol. 93-29, Electrochem. Soc., Pennington, 1993.

- [8] H. Baumgart, Ch. Hunt, S. Iyer, U. Gösele, T. Abe (Eds.), Third Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 95-7, Electrochem. Soc., Pennington, 1995.

- [9] U. Gösele, H. Baumgart, Ch. Hunt, T. Abe (Eds.), Fourth Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 97-36, Electrochem. Soc., Pennington, 1998.

- [10] J. Haisma, B.A.C.M. Spierings, U.K.P. Biermann, J.A. Pals, Siliconon-insulator wafer bonding—wafer thinning technological evaluations, Jpn. J. Appl. Phys. 28 (1989) 1426–1443.

- [11] W.P. Maszara, Silicon-on-insulator by wafer bonding: a review, J. Electrochem. Soc. 138 (1991) 341–347.

- [12] P.W. Barth, Silicon fusion bonding for fabrication of sensors, actuators and microstructures, Sensors and Actuators A21–A23 (1990) 919–926.

- [13] Ch. Harendt, H.-G. Graf, B. Höfflinger, E. Penteker, Review: silicon fusion bonding and its characterization, J. Micromech. Microeng. 2 (1992) 113–116.

- [14] F.S. d'Aragona, Lj. Ristic, Silicon direct wafer bonding, in: Lj. Ristic (Ed.), Sensor Technology and Devices, Chap. 5, Artech House, Boston, 1994, pp. 157–201.

- [15] U. Gösele, Q.-Y. Tong, Semiconductor wafer bonding, Annu. Rev. Mater. Sci. 28 (1992) 215–241.

- [16] Special Issue on Direct Bonding, Philips J. Res. 49 (1995) 1-182.

- [17] Q.-Y. Tong, U. Gösele, Semiconductor Wafer Bonding: Science and Technology, VCH-Wiley, New York, 1998, in press.

- [18] R. Stengl, K.-Y. Ahn, U. Gösele, Bubble-free silicon wafer bonding in a non-cleanroom environment, Jpn. J. Appl. Phys. 27 (1988) L2364–L2366.

- [19] W.P. Maszara, G. Goetz, A. Caviglia, J.B. McKitterick, Bonding of silicon wafers for silicon-on-insulator, J. Appl. Phys. 64 (1988) 4943–4950.

- [20] G. Cha, R. Gafiteanu, Q.-Y. Tong, U. Gösele, Design considerations for wafer bonding of dissimilar materials, in: H. Baumgart, Ch. Hunt, M. Schmidt, T. Abe (Eds.), Second Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 93-29, Electrochem. Soc., Pennington, 1993, p. 257–266.

- [21] K. Ljungberg, A. Söderbärg, Y. Bäcklund, Spontaneous bonding of hydrophobic silicon surfaces, Appl. Phys. Lett. 62 (1993) 1363– 1365.

- [22] Q.-Y. Tong, E. Schmidt, U. Gösele, M. Reiche, Hydrophobic wafer bonding, Appl. Phys. Lett. 64 (1994) 625–627.

- [23] Q.-Y. Tong, U. Gösele, Thickness considerations in silicon wafer direct bonding, J. Electrochem. Soc. 142 (1995) 3975–3979.

- [24] Q.-Y. Tong, W.J. Kim, T.-H. Lee, U. Gösele, Low vacuum wafer bonding, Electrochem. Solid-State Lett. 1 (1998) 52–53.

- [25] O. Zucker, W. Langheinrich, M. Kulozik, Application of oxygen plasma processing to silicon direct bonding, Sensors and Actuators 36 (1993) 227–231.

- [26] S. Farrens, J.R. Dekker, J.K. Smith, B.F. Roberds, Chemical free room temperature wafer to wafer direct bonding, J. Electrochem. Soc. 142 (1995) 3949–3955.

- [27] M. Reiche, K. Gutjahr, D. Stolze, D. Burczyk, M. Petzold, The effect of plasma treatment on the Si/Si bonding behaviour, in: U. Gösele, H. Baumgart, Ch. Hunt, T. Abe (Eds.), Fourth Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 97-36, Electrochem. Soc., Pennington, 1998, pp. 437–444.

- [28] G. Kräuter, A. Schumacher, U. Gösele, Low temperature silicon direct bonding for application in micromechanics: bonding energies for different combinations of oxides, Sensors and Actuators A 70 (1998) 271–275.

- [29] T. Abe, M. Nakano, T. Itoh, Silicon wafer-bonding process technol-

ogy for SOI structures, in: Proc. 4th. Int. Symp. Silicon-on-insulator Technologies and Devices, Electrochem. Soc. Proc., Vol. 90-6, 1990, pp. 61–71.

- [30] M.K. Weldon, Y.J. Cabal, D.R. Hamann, S.B. Christman, E.E. Chaban, L.C. Feldman, Physics and chemistry of silicon wafer bonding investigated by infrared absorption spectroscopy, J. Vac. Sci. Technol. B 14 (1996) 3095–3106.

- [31] S. Mack, H. Baumann, U. Gösele, Gas development at the interface of directly bonded silicon wafers: investigations on silicon-based pressure sensors, Sensors and Actuators A 56 (1996) 273–277.

- [32] S. Mack, H. Baumann, U. Gösele, H. Werner, R. Schlögl, Analysis of bonding-related gas enclosure in micromechanical cavities sealed by silicon wafer bonding, J. Electrochem. Soc. 144 (1997) 1106– 1111.

- [33] G. Wallis, D.I. Pomerantz, Field assisted glass-metal sealing, J. Appl. Phys. 40 (1969) 3946–3949.

- [34] U. Gösele, H. Stenzel, T. Martini, J. Steinkirchner, D. Conrad, K. Scheerschmidt, Self-propagating room-temperature silicon wafer bonding in ultrahigh vacuum, Appl. Phys. Lett. 67 (1995) 3614– 3616.

- [35] A. Plössl, R. Scholz, J. Bagdahn, H. Stenzl, K.N. Tu, U. Gösele, The interface of silicon samples joined at room temperature by wafer direct bonding in ultrahigh vacuum, Electrochem. Soc. Proc. 97-36 (1998) 1361–1372.

- [36] T. Abe, A. Uchiyama, Y. Nakazoto, Wafer thinning without an etchstop down to 0.1 μm, in: U. Gösele, J. Haisma, M. Schmidt, T. Abe (Eds.), First Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 92-7, Electrochem. Soc., Pennington, 1992, pp. 200–210.

- [37] S.S. Iyer, P.M. Pitner, M.J. Tejwani, T.O. Sedgwick, Ultra thin silicon-on-insulator using epitaxial etch stops, in: H. Baumgart, Ch. Hunt, M. Schmidt, T. Abe (Eds.), Second Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 93-29, Electrochem. Soc., Pennington, 1993, pp. 3–16.

- [38] S. Yonehara, K. Sakaguchi, N. Sato, Epitaxial layer transfer by bond and etch back of porous silicon, Appl. Phys. Lett. 64 (1994) 2108–2110.

- [39] M. Bruel, A new silicon on insulator material technology, Electron. Lett. 31 (1995) 1201–1202.

- [40] M. Bruel, B. Aspar, A.J. Auberton-Herve, Smart-cut: a new silicon on insulator material technology based hydrogen implantation and wafer bonding, Jpn. J. Appl. Phys. 36 (1997) 1636–1641.

- [41] Q.-Y. Tong, R. Scholz, U. Gösele, T.-H. Lee, L.-J. Huang, Y.-L. Chao, T.Y. Tan, A 'smarter-cut' approach to low temperature silicon layer transfer, Appl. Phys. Lett. 72 (1998) 49–51.

- [42] L. Di Cioccio, Y. Le Tiec, F. Letertre, C. Jaussaud, M. Bruel, Silicon carbide on insulator formation by the smart cut process, Electron. Lett. 32 (1996) 1144–1145.

- [43] Q.-Y. Tong, K. Gutjahr, S. Hopfe, U. Gösele, T.-H. Lee, Layer splitting process in hydrogen-implanted Si, Ge, SiC, and diamond substrates, Appl. Phys. Lett. 70 (1997) 1390–1392.

- [44] E. Jalaguier, B. Aspar, S. Pocas, J.F. Michaud, M. Zussy, A.M. Papon, M. Bruel, Transfer of 3 inch GaAs film on silicon substrate by proton implantation process, Electron. Lett. 34 (1998) 408–409.

- [45] G.P. Imthurn, G.A. Garcia, H.W. Walker, L. Forbes, Bonded silicon-on-sapphire wafers and devices, J. Appl. Phys. 72 (1992) 2526– 2527.

- [46] K. Eda, A. Kanaboshi, T. Ogura, Y. Taguchi, Quartz crystal on silicon technique using direct bonding, in: H. Baumgart, Ch. Hunt,

M. Schmidt, T. Abe (Eds.), Second Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 93-29, Electrochem. Soc., Pennington, 1993, pp. 373– 381.

- [47] Q.-Y. Tong, U. Gösele, T. Martini, M. Reiche, Ultrathin singlecrystalline silicon on quartz (SOQ) by 150°C wafer bonding, Sensors and Actuators A 48 (1995) 117–123.

- [48] V. Lehmann, K. Mitani, R. Stengl, T. Mii, U. Gösele, Bubble-free wafer bonding of GaAs and InP on silicon in a microcleanroom, Jpn. J. Appl. Phys. 28 (1989) L2141–L2143.

- [49] G.G. Goetz, Generalized reaction bonding, in: U. Gösele, J. Haisma, M. Schmidt, T. Abe (Eds.), First Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 92-7, Electrochem. Soc., Pennington, 1992, pp. 65–72.

- [50] P. Kopperschmidt, S. Senz, G. Kästner, D. Hesse, U.M. Gösele, Materials integration of gallium arsenide and silicon by wafer bonding, Appl. Phys. Lett. 72 (1998) 3181–3183.

- [51] R.J. Ram, L. Yang, K. Nauka, M. Houng, M. Ludowise, D.E. Mars, J.J. Dudley, S.Y. Wang, Analysis of wafer fusing for 1.3 micrometer vertical cavity surface emitting lasers, Appl. Phys. Lett. 62 (1993) 2474–2476.

- [52] F.A. Kish, D.A. Vanderwater, I.-H. Tan, G.E. Hofler, D.C. DeFevere, Application of Wafer Bonding to the Fabrication of Light-Emitting Diodes, in: U. Gösele, H. Baumgart, Ch. Hunt, T. Abe (Eds.), Fourth Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 97-36, Electrochem. Soc., Pennington, 1998, pp. 25–36.

- [53] Z.L. Liau, D.E. Mull, Wafer fusion: a novel technique for optoelectronic device fabrication and monolithic integration, Appl. Phys. Lett. 56 (1990) 737–739.

- [54] Y.H. Lo, Z.H. Zhu, Y. Qian, F.E. Ejeckham, G.L. Christenson, Wafer bonding technology and its optoelectronic applications, SPIE Proc. 3006 (1997) 26–35.

- [55] W.G. Easter, G.T. Jones, R.H. Shanaman, C.A. Goodwin, Polysilicon to silicon bonding in laminated dielectrically isolated (LDI) wafers, in: U. Gösele, J. Haisma, M. Schmidt, T. Abe (Eds.), First Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 92-7, Electrochem. Soc., Pennington, 1992, pp. 223–229.

- [56] P. Kopperschmidt, G. Kästner, D. Hesse, Recent developments in semiconductor-on-sapphire wafer bonding, in: U. Gösele, H. Baumgart, Ch. Hunt, T. Abe (Eds.), Fourth Int. Symp. Semiconductor Wafer Bonding: Science, Technology and Applications, Electrochem. Soc. Proc., Vol. 97-36, Electrochem. Soc., Pennington, 1998, pp. 176–186.

- [57] P. Kopperschmidt, G. Kästner, D. Hesse, U. Gösele, Wafer bonding of gallium arsemide on sapphire, Appl. Phys. A 64 (1997) 533–537.

Ulrich M. Gösele is director at the Max Planck Institute of Microstructure Physics, Halle, Germany since 1993. For many years he was J.B. Duke Professor of Materials Science at Duke University in North Carolina, and before at Siemens Research Laboratories in Munich. He had visiting appointments at IBM's Watson Research Center, NTT LSI Laboratories in Atsugi, Japan, as well as the Atomic Energy Board in South Africa. His research interests include defects and diffusion process in semiconductor, quantum effects in porous silicon, self-organized structure formation and semiconductor wafer bonding. He holds numerous patents on wafer bonding technology and has co-organized various symposia in this field. Together with Q.-Y. Tong, he wrote the first book on semiconductor wafer bonding.